There are two Namco 07xx custom chips in Pole Position: one on the CPU board and one on the video board. They perform the same function on each board, which is to determine the exact position of the CRT beam.

Only the 07xx on the video board is directly related to the CRT beam position. The 07xx chip on the CPU board merely reproduces the same information so the CPUs and connected electronics may coordinate activities and not interfere with the video rasterization. For example, we know from a previous article that the 07xx horizontal position bit 1 (signal 2H) is used to insert wait states for the Z8002 CPUs.

Chip Operation

A simple experimental setup was performed by powering up a sample 07xx chip on a breadboard with:

- +5V and GND on pins 28 and 14,

- GND on pin 15,

- 1k pull-up resistors on /HRESET and /VRESET pins 13 and 16, and

- 6.144 MHz clock driven on pin 1.

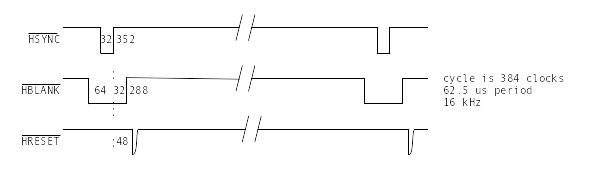

Horizontal Outputs

The horizontal outputs are expressed in terms of clock cycles.

The instantaneous horizontal position is expressed by a nine-bit counter with output signals 256H, 128H, 64H, 32H, 16H, 8H, 4H, 2H and 1H. In more modern terms the signals might be called HPOS[8:0].

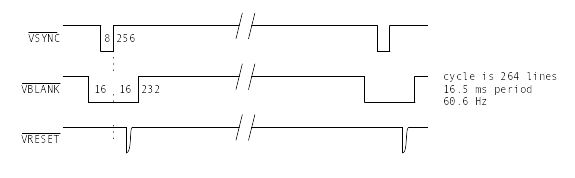

Vertical Outputs

The vertical outputs are expressed in terms of horizontal lines.

The current vertical line is expressed by an eight-bit counter with output signals 128V, 64V, 32V, 16V, 8V, 4V, 2V, and 1V. In more modern terms the signals might be called VPOS[7:0].

Alignment Observations

Transitions on horizontal signals occur (after propagation delay) with the rising edge of the input clock.

/HRESET appears to reset the horizontal count to zero.

Transitions on vertical signals occur with the rising edge of /HSYNC.

/VRESET appears to load the vertical count to eight. Importantly, this ensures the 128V signal transitions 0->1 at the midpoint of the screen (ie. halfway between /VBLANK pulses).

Both /HRESET and /VRESET are open-collector I/O, and are connected between 07xx chips. This accomplishes the synchronization between the chips. /HRESET and /VRESET appear to operate independently. Whether they are synchronous to the CLK input or operate asynchronously has not been tested.

Summary

The Namco 07xx chip generates and synchronizes raster signals and beam position counters based on a 384 pixel wide by 264 line tall cycle. Of this, lines 16..239 are registered when /VBLANK is not asserted.

Pixel positions 368..383,0..271 (per line), are registered when /HBLANK is not asserted. Of these, apparently only pixels 0..255 are actually active, with 16 pixels on each side of that area inactive.